\_\_\_\_\_

# 21 Level Asymmetric Inverter without Inversion Circuit with Reduced Switch Count for BLDC Motor Drive

[1]Amit B. Jadhav, [2]Dr. Mahadev S. Patil

Assistant Professor, Department of Electrical Engineering, Annasaheb Dange College of Engineering & Technology, Ashta, Sangli, Maharashtra, India

Professor & Head, Department of Electronics and Telecommunication Engineering, Rajarambapu Institute of Technology, Skharale, Sangli, Maharashtra, India

**Abstract -** Design for asymmetrical Multi-Level Inverter without H-bridge and with minimal number of switch is presented in this paper. The proposed circuit is capable of generating 21 levels with only 10 switches and 3 unequal D.C.voltage sources. Operation of the proposed circuit is discussed in detail in this paper and there by framing the switching sequence for the proposed circuit. Simulation of the presented inverter is done for loads like resistive, reactive and induction motor. From the simulation results, inverter performance is analyzed in terms of THD.

**Keywords** - Asymmetric inverter, modes of operation, multi-level inverter, power electronics, reduced switch component.

#### 1. Introduction

Multi-Level Inverters (MLI) have become a revolutionin the world of power electronics for its improved voltage and current waveforms, high power applications and for power quality demanding applications. They also find applications in speed drive control, STATCOMS, HVDC and HVACtransmissions. The advantages of multi-level inverters are used in higher voltage operability, reduced voltage derivatives, reduced voltage harmonic components, fault tolerant operation and increased efficiency. The current trend applications for multi-level inverters are around photovoltaic conversions, electric vehicle technology, wind energy technology etc. Multi- level inverter consists of various circuit components such as diodes, voltage sources and switches. Based on the construction of the circuit and the voltage sources considered, the inverters are classified as symmetric and asymmetric MLIs and to be specific they are further classified as cascaded H-Bridge, diode clamped and flyingcapacitor inverters [1]-[2].

In symmetric MLIs, the D.C. sources have the same amplitude in their configuration, whereas in asymmetrical inverters the sources have non identical source ratings in their configuration. All these types of conventional type MLIs have a greater number of switches in their design which directed to construct MLI with reduced components. As reduced number of switches is required, asymmetrical MLIs are identified foroperation. Due to the reduced switch count, the switching power losses are lowered drastically.

Also, another big advantage of asymmetrical configuration is that for the same switch count, higher level can be obtained in asymmetrical configuration compared to symmetrical configuration. Required parameters for the design of a MLI are number of levels to be acquired, count of the switches needed for the required levels, harmonic occupancy in voltage obtained at output, the count of independent D.C. sources needed to generate the required +levels, switch stress and the standing voltage.

However, for achieving higher unit steps, more oflevels, a greater quantity of switches are required. So, a solution is needed to have additional levels and to have reduced switching components [3]-[6]. For better performance of the MLI, the harmonic distortion finds a crucial role. The achievement of the MLI can be inferred from the amount of harmonic distortion present at the loadcurrent and voltage. The harmonic distortion must be reduced so that the MLI performance can be improved. Forthe reduction of harmonic distortion, the PWM techniquesengaged in the semiconductor switches plays a central role. This also helps in providing the required switching patternsuch that we get a sinusoidal wave across the load.

Considering the above, many attempts are being made in the past few years to reduce the switch count and those works are discussed in [7]-[11]. These works have given some new structures and topologies with reduced count but having its own shortcomings. The proposed model is also a new topology structure with reduced switchingcomponent and taken into consideration of the shortcomings to produce a much higher level of output. The proposed model is a new topology for 21-level asymmetric MLI with only 10 switches and 3 unequal D.C. sources. The configuration does not possess inversion circuit, there by operability of the circuit is increased for higher range of voltages.

This paper follows through as given in section II describes the model of proposed circuit, the analysis of switch count, level count and the peak voltage followed by section III which provides the working, modes of operation and the switching sequence of the proposed circuit in a detail manner. Section IV is the results of the proposed model from the simulation. Finally in Section V, conclusions are made on the proposed model which gives ahigher voltage with reduced switch count and reduced THD.

## 2. 21-Level Inverter With Switching Sequence

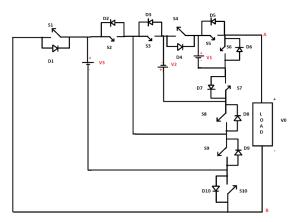

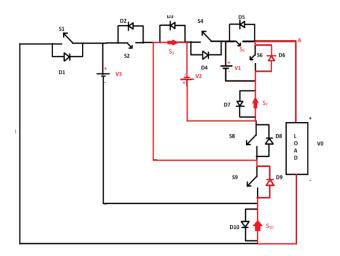

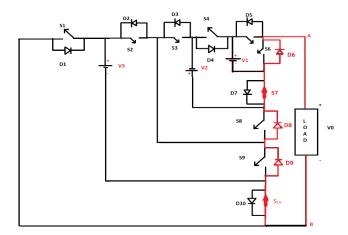

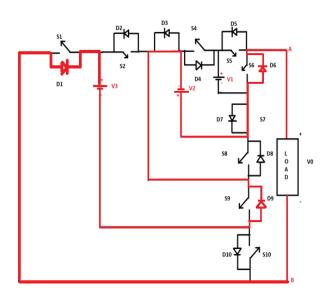

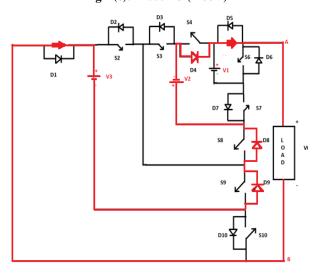

A MLI configuration without inversion circuit is shown in figure 1. To obtain 21 levels, the proposed circuit consists of 10 switches and 3 voltage sources. Here, all 10 switches are uni-directional in nature as illustrated in figure 2, so that identical driver circuit is used for the switches present in the circuit. A basic sinusoidal PWM technique is used generating triggering pulses for the proposed model. The designed MLI circuit is formed with 3 unequal voltage sources which will make an asymmetric configuration. D.C. voltage sources are identified as 40V, 80V and 280V respectively.

## A. MLI Design Criteria

For the inverter topology, mathematical equation is derived with the aim of finding the level count obtained from the inverter and switch count and the voltage sources required for the inverter. Let the voltage sources required be switch count be  $N_{SW}$ , level count of the inverter be  $N_{IVI}$ .

Fig 1: 21 Level Inverter [12]

Fig 2: Switch Configuration

The switch count for the proposed inverter can becalculated as given in Equation 1,

Nsw = 2m + 2-----(1)

The level count for the figure 1 can be calculated fromEquation2,

$Nlvl = 7 \times m$  -----(2)

The peak output voltage of the inverter is achieved from Equation 3,

$V0, max = (2m + 2) \times VDC$  -----(3)

Now the proposed topology consists of 3 voltage sources (m = 3), so switch count  $N_{SW} = 10$ , the level count of the inverter is  $N_{lVl} = 21$ . Here the VDC = V1 = 40V, so the peak output voltage can be given as V0, max = 400V.

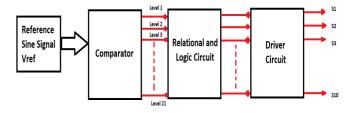

### B. Pulse Generation

The pulses that are to be given to the switches are generated by using four divisions, sine wave signal as reference, comparator for comparing the reference wave and the gain, relational and logic circuit are used for producing the pulses for the switches and driver circuits for the triggering of the switches. These four divisions canbe demonstrated as illustrated in figure 3.

Fig 3: Various Divisions of Pulse Generation

From the block diagram (Figure 3), a sine wave is taken as reference and the amplitude of the reference wave is taken as 11V. Its chosen based on the positive level and zero level needed for the MLI. This reference wave is given as the input to the comparator. The output of the comparator obtained is directed to relational and logiccircuit block. Here relational operators are used to comparethe levels that are to be selected. For each level a pair of relational operators and an AND gate is used for the generation of the pulses. This output is sent to a driver circuit which consists of a sum block and multiport switch block. The sum block collects all the pulses that is to be selected for each switching sequence. The multiport block is used to provide the switching sequence in which the switches are to be turned on. For each level the multiport block is coded with switching sequence of the respective level as its input. Now all the four divisions are implemented for each level coded with their respective switching sequence and then given to the IGBT switches used in the proposed configuration.

# 3. Modes Of Operation

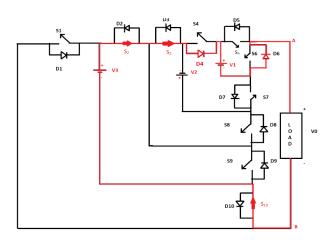

The inverter is designed to work in 21 modes of operation to construct an alternating waveform. For understanding purpose; few modes are explained in figure 3 Device status for each mode of operation is given below,

Mode-1:S2, S3, S5, S7, S10 devices are 'ON' to generate400V

Mode-2: S2, S3, S6, S7, S10 devices are 'ON' to generate 360V

Mode-3: S2, S5, S7, S8, S10 devices are 'ON' to generate 320V

Mode-4: S2, S3, S4, S5, S10 devices are 'ON' to generate 280V

Mode-5:S2, S3, S4, S6, S10 devices are 'ON' to generate 240V

Mode-6:S1, S3, S6, S7, S9 devices are 'ON' to generate 200V

Mode-7:S2, S4, S6, S8, S10 devices are 'ON' to generate 160V

Mode-8:S3, S5, S7, S9, S10 devices are 'ON' to generate120V

Mode-9:S9, S6, S7, S9, S10 devices are 'ON' to generate 80V

Mode-10:S5, S7, S8, S9, S10 devices are 'ON' to generate40V

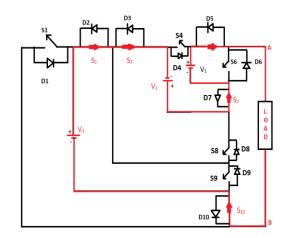

Mode-11:S6, S7, S8, S9, S10 devices are 'ON' to generate 0V

Mode-12:S3, S4, S6, S9, S10 devices are 'ON' to generate -40V

Mode-13:S4, S5, S8, S9, S10 devices are 'ON' to generate -80V

Mode-14:S4, S6, S8, S9, S10 devices are 'ON' to generate -120V

Mode-15:S1, S3, S5, S7, S9 devices are 'ON' to generate -160V

```

Mode-16:S1, S3, S6, S7, S9 devices are 'ON' to generate -200V Mode-17:S1, S5, S7, S8, S9 devices are 'ON' to generate -240V Mode-18:S1, S6, S7, S8, S9 devices are 'ON' to generate -280V Mode-19:S1, S3, S4, S6, S9 devices are 'ON' to generate -320V Mode-20:S1, S4, S5, S8, S9 devices are 'ON' to generate -360V Mode-21:S1, S4, S6, S8, S9 devices are 'ON' to generate -400V

```

From the modes of operation, the Table 1 is arrived to show the switching sequence for the different levels of theinverter.

Levels Mode  $S_{10}$  $V_{o}$  $\tilde{\mathbf{s}}$  $\mathbf{z}$  $\mathbf{S}_2$  $\mathbf{S}_{3}$  $^{2}$  $S_{5}$ Š  $S_7$ Š +400V+360V+320V +280V +240V+200V+160V +120V+80V +40V0V-1 -40V -2 -80V -3 -120V -4 -160V -5 -200V -240V -6 -7 -280V -8 -320V -9 -360V -10 0 0 -400V

**Table 1:** Sequence for the switches

**Fig 4 (a):** Mode-1 (+400V)

**Fig 4(b):** Mode-5 (+240V)

**Fig 4(c):** Mode-9 (+80V)

**Fig 4(d):** Mode-11 (0V)

**Fig 4(e):** Mode-16 (-200V)

**Fig 4 (f):** Mode-20 (-360V)

Fig 4: Modes of Operation for 21 level inverters

# 4. Simulation And Results

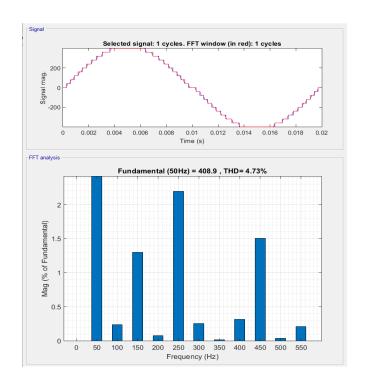

In figure 4, the simulated result of the proposed inverter simulated in MATLAB/SIMULINK with resistive load of  $150\Omega$  is shown. THD of the inverter's voltage wave shape is 4.73% and it is inside the scope of guidelines given in IEEE 519. The proposed circuit constructs a crest-to-crest voltage of  $\pm 400$ V as illustrated in figure 4.

Fig 5 (a): Simulation result of 21-level inverter forRload

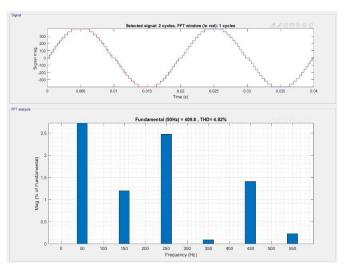

Further,the proposed circuit is simulated for a R-L load, with R=150 $\Omega$ , L = 0.477H. The output voltage for the RL load for the proposed inverter is displayed in figure 5 and the THD for the presneted inverter's output voltage is4.82%.

Fig 5(b): Results of the circuit tied with RL Load of 21-level inverter (Voltage THD)

Fig 5(c). Results of the circuit tied with RL Load of 21-level inverter (Current THD)

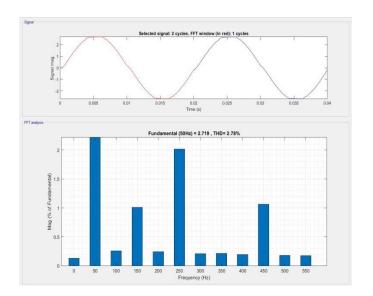

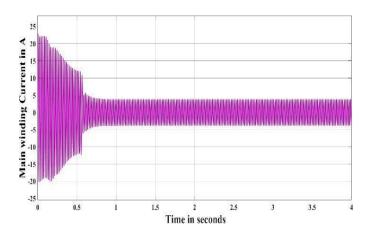

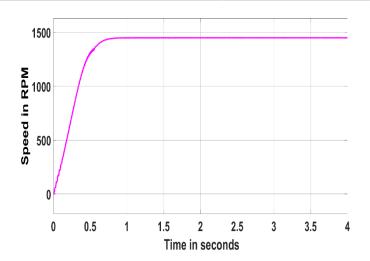

The proposed circuit is also simulated for inductionmotor load as given in the below figure,

Fig 5(d). Results of the circuit tied with inductionmotor Load of 21-level inverter (main winding current)

Fig 5(e). Results of the circuit tied with inductionmotor Load of 21-level inverter (Speed)

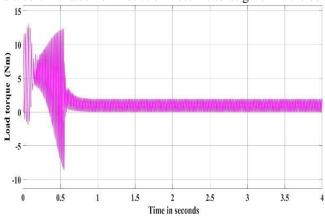

Fig 5(f). Results of the circuit tied with induction motor Load of 21-level inverter (Load torque)

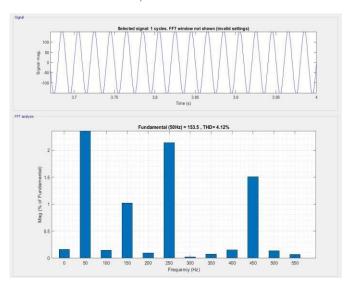

When the circuit is tied with an induction motor, the motor settles at a speed of 1451 rpm, due to a load torque of 2 Nm, as presented in figures 5e and 5f respectively. Now the THD of the circuit after connecting it with a motorload is 4.12% that can be shown as,

Fig 5(g). Results of the circuit tied with induction motor Load of 21-level inverter (Voltage THD)

# 5. Comparative Study

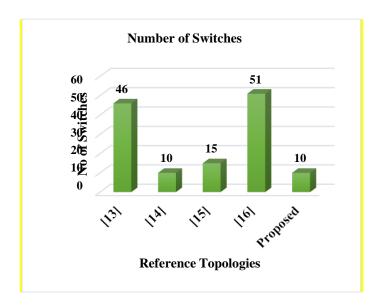

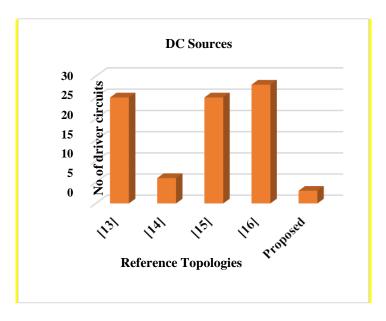

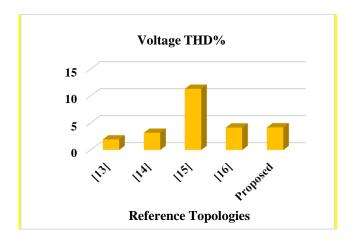

Multiple structures for the MLI have been presented to reduce the switch count. The structure realized in [13] is a 51-level symmetric structure consisting of 9 level structures in cascade with an H-bridge circuit. This structure has 25 independent sources, each having a magnified of 1 volt, along with 46 power switches. Due to the symmetrical structure, achieved output voltage is less, but the circuit has a low THD value of 1.95%. The proposed MLI in [14] 31-levels are obtained using asymmetric configuration. This configuration consists of ten power switches and six independent sources. The negative levels obtained using an H-bridge and the THD value obtained for reactive load is 3.18%. By using the basic principle of CHB inverters, a new cascaded topology is realized in [15]. The basic unit is made of 3 independent sources and 5 power switches. This basic units cascaded with H-bridge to obtain multiple levels. Using one base unit 9 levels are achieved with a THD value of 18.8%. Cascading two basic units we obtain 15 levelswith a THD value of 14.16%. By cascading the basic unit, we get the respective levels as 27, 33, 39 and their respective THD values are 12.07, 11.85 and 11.33%. In [16] 57-level inverter is realized having 9 cascaded structures with an H-bridge. The basic unit

consists of 3 independent sources and 6 power switches. The symmetric configuration consists of a total switch count of 51 and 28 independent sources to obtain the 57-level output. Also, the same levels of output can be obtained in an asymmetrical configuration with only two basic units where the switch count is 18 and the number ofindependent sources is seven. Comparative plot on switch count, independent source and THD% for the reference paper [13]–[16] with respective to propose topology is shown in figure 6(a), figure 6(b) and figure 6(c) respectively.

Fig 6(a). Comparative study for switch count

Fig 6(b). Comparative study for independentsources

Fig 6(c). Comparative study for THD%

# 6. Conclusion

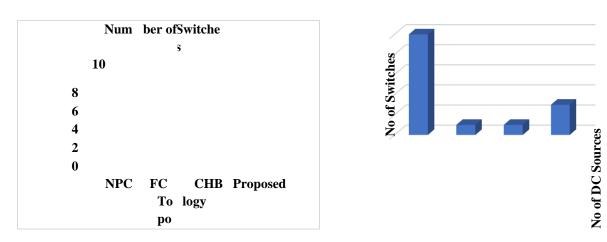

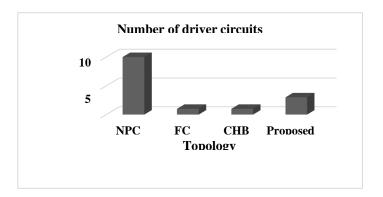

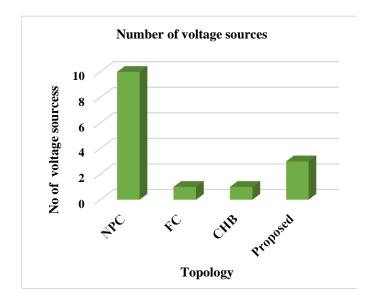

A 21-levelconfiguration of MLI which make use of minimal switch count has been discussed in detail in this paper. The proposed circuit can achieve the maximum voltage with minimum number of switches with a low THD, thereby reducing the cost and size. Comparison between the proposed circuit with traditional inverters such as cascaded H-Bridge, diode clamped and flying capacitor inverters are demonstrated from figure 7 (a) to figure 7 (e).

Fig 7(a). Number of Switches

Fig 7(b). Number of driver circuits

Fig 7(c). Number of voltage sources

### References

- [1] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," IEEE Trans. Power Electron., vol. 31, no. 1, pp. 135–151, Jan. 2016.

- [2] G. K. Srinivasan, M. Rivera, V. Loganathan, D. Ravikumar, and B. Mohan, "Trends and Challenges in Multi-Level Inverter with Reduced Switches," Electronics, vol. 10, no. 4, p. 368, Feb. 2021.

- [3] L. Vijayaraja, S. G. Kumar and M. Rivera, "A New Topology of Multilevel Inverter with Reduced Part Count," 2018 IEEE International Conference on Automation/XXIII Congress of the Chilean Association of Automatic Control (ICA-ACCA), 2018, pp. 1-5, doi: 10.1109/ICA-ACCA.2018.8609742.

- [4] Z. E. Abdulhamed, A. H. Esuri and N. A. Abodhir, "New Topology Of Asymmetrical Nine-Level Cascaded Hybrid Bridge Multilevel Inverter," 2021 IEEE 1st International Maghreb Meeting of the Conference on Sciences and Techniques of Automatic Control and Computer Engineering MI-STA, 2021, pp. 430-434, doi: 10.1109/MI-STA52233.2021.9464511.

- [5] Sheikh Tanzim Meraj, Nor Zaihar Yahaya, Kamrul Hasan, Ammar Masaoud, A hybrid T-type (HT-type) multilevel inverter with reduced components, Ain Shams Engineering Journal, Volume 12, Issue 2,2021, Pages 1959-1971, ISSN 2090-4479.

- [6] P. Ponnusamy et al., "A New Multilevel Inverter Topology With Reduced Power Components for Domestic Solar PV Applications," in IEEE Access, vol. 8, pp. 187483-187497, 2020, doi: 10.1109/ACCESS.2020.3030721.

- [7] B. Ganesh et al., "Implementation of Twenty seven level and Fifty one level Inverter using constant voltage sources," 2019 IEEE CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), 2019, pp. 1-4, doi: 10.1109/CHILECON47746.2019.8987978.

- [8] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal and M. A. Memon, "A New Multilevel Inverter Topology With Reduce Switch Count," in IEEE Access, vol. 7, pp. 58584-58594, 2019.

- [9] M. D. Siddique, S. Mekhilef, N. M. Shah and M. A. Memon, "Optimal Design of a New Cascaded Multilevel Inverter Topology With Reduced Switch Count," in IEEE Access, vol. 7, pp. 24498- 24510, 2019, doi: 10.1109/ACCESS.2019.2890872.

- [10] E. Samadaei, S. A. Gholamian, A. Sheikholeslami and J. Adabi, "An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters With Reduced Components," in IEEE Transactions on

\_\_\_\_\_

- Industrial Electronics, vol. 63, no. 11, pp. 7148-7156, Nov. 2016, doi: 10.1109/TIE.2016.2520913.

- [11] V. Loganathan, G. K. Srinivasan, and M. Rivera, "Realization of 485 Level Inverter Using Tri-State Architecture for Renewable Energy Systems," Energies, vol. 13, no. 24, p. 6627, Dec. 2020.

- [12] S. R. Khasim, D. C, S. Padmanaban, J. B. Holm-Nielsen and M. Mitolo, "A Novel Asymmetrical 21-Level Inverter for Solar PV Energy System With Reduced Switch Count," in IEEE Access, vol. 9, pp. 11761-11775, 2021, doi: 10.1109/ACCESS.2021.3051039.

- [13] B. Ganesh et al., "Implementation of Twenty seven level and Fifty one level Inverter using constant voltage sources," 2019 IEEE CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), 2019, pp. 1-4, doi: 10.1109/CHILECON47746.2019.8987978.

- [14] G. Raman, A. Imthiyas, M. D. Raja, L. Vijayaraja and S. G. Kumar, "Design of 31-level Asymmetric Inverter with Optimal Number of Switches," 2019 IEEE International Conference on Intelligent Techniques in Control, Optimization and Signal Processing (INCOS), 2019, pp. 1-3, doi: 10.1109/INCOS45849.2019.8951354.

- [15] S. Ponkumar, S. M. Rivera, F. Kamroon and S. G. Kumar, "Realization of cascaded multilevel inverter," 2017 CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), 2017, pp. 1-7, doi: 10.1109/CHILECON.2017.8229701.

- [16] L. Vijayaraja, V. Nandhinipriya, R. Dhanasekar, S. G. Kumar and M. Rivera, "Simulation and Experimentation of 57-Level Inverter," 2021 IEEE International Conference on Automation/XXIV Congress of the Chilean Association of Automatic Control (ICA-ACCA), 2021, pp. 1-8, doi: 10.1109/ICAACCA51523.2021.9465284.